组合电路设计与测试

实验目的

- 熟练组合电路的设计和实现的方式

- 掌握Verilog HDL组合电路模块的设计规范。

- 掌握组合逻辑测试代码的撰写和仿真测试方法。

预习要求

- 了解assign、门原件、always过程语句及模块调用描述组合逻辑电路设计的方法和注意事项。

- 了解QuartusII或iverilog>kwave软件使用的基本规范和操作流程

实验原理

带优先级8-3编码器和3-8译码器

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19# 带优先级8-3编码器

module code83(in8,out3);

input[7:0] in8; output reg[2:0] out3;

always@(in8)

begin

case(in8)

if(in8[7]) out3=3'b111;

else if(in8[6]) out3=3'b110;

else if(in8[5]) out3=3'b101;

else if(in8[4]) out3=3'b100;

else if(in8[3]) out3=3'b011;

else if(in8[2]) out3=3'b010;

else if(in8[1]) out3=3'b001;

else if(in8[0]) out3=3'b000;

else out3=3'bxxx;

endcase

end

endmodule1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18# 3-8译码器

module decode38(in3,out8);

input[2:0] in3; output[7:0] out8;

always@(in3)

begin

case(in3)

3'd0:out=8'b00000001;

3'd1:out=8'b00000010;

3'd2:out=8'b00000100;

3'd3:out=8'b00001000;

3'd4:out=8'b00010000;

3'd5:out=8'b00100000;

3'd6:out=8'b01000000;

3'd7:out=8'b10000000;

default:out=8'bxxxxxxxx;

endcase

end

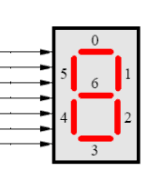

endmodule七段管的工作逻辑

一个七段管使用7bit信号控制7段LED灯的亮灭。若每段LED灯赋值为0,灯亮;赋值为1时灯灭。则Hex=7‘b1111001,其中hex[6]—hex[5]…..hex[0]分别对应下图1中七段管中的编号是6543210的信号。那么该信号hex[6]=1 hex[5]=1 hex[4]=1 hex[3]=1 hex[2]=0 hex[1]=0 hex[0]=1

实验内容

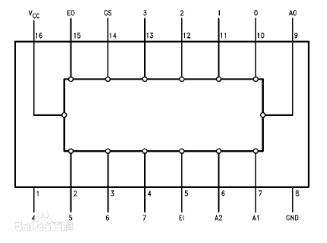

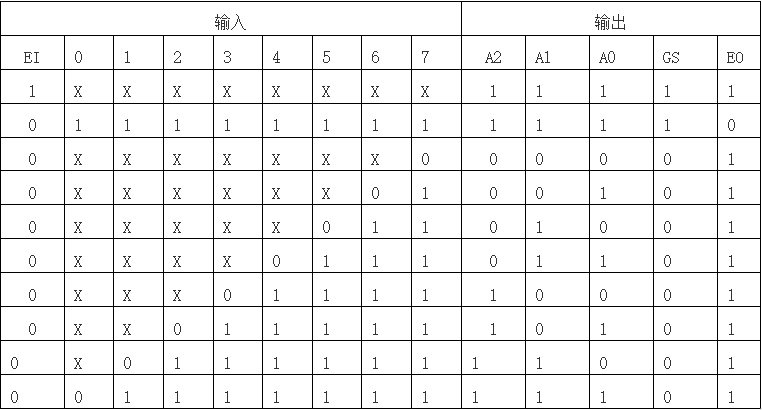

- 用verilog实现74LS148的功能定义并测试。

74LS148是带有扩展功能的8-3线优先编码器,它有8个信号输入端,3个二进制码输出端(0-7),一个输入使能端(EI),一个选通输出端()和一个扩展端。使能端为“0”时,该芯片被选中,否则不被选中。选通输出端和扩展端主要用于功能扩展。

0-7 编码输入端(低电平有效)

EI 选通输入端(低电平有效)

A0、A1、A2 三位二进制编码输出信号即编码 输 出 端(低电平有效)

GS 片优先编码输出端即宽展端(低电平有效)

EO 选通输出端,即使能输出端 - 将8个拨动开关作为8位并行输入,即对应数码为0000_0000—-1111_1111,十进制数值为0-255,将编码对应的十进制数值显示在三个七段管上。比如若输入1000_0100对应十进制数为132,则在三个七段上显示1、3、2数字。建议七段管显示译码电路设计成模块,主模块采用模块调用的方式实现3个七段管的驱动。

实验要求

- 按照上面的提示完善报告

- 将程序编译过程中出现的主要错误及解决方案进行总结

- 掌握和练习数字系统的分析步骤,并将一些核心步骤进行记录

- 将编写的程序与仿真结果进行记录

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 QXA!

评论